經過上一篇的RSA撰寫的經驗,對於其他加解密應該有不錯的想法,這一篇將要做AES128位元,不同RSA32位元,就來試試看吧。

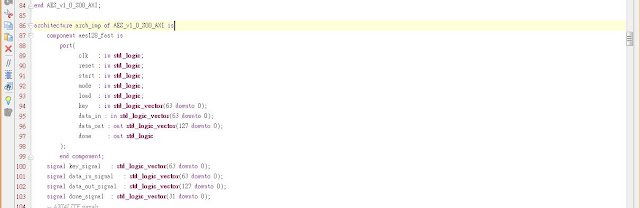

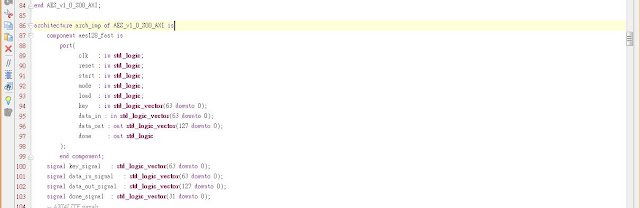

AES 最TOP檔部分程式碼

跟上一篇一樣先來創建IP哦,但是這次要13個暫存器,因為1個IP得Data width只能傳輸32位元,所以超過就要拆開來去分配,key data_in各2個 data_out需要4個。

照慣例匯入source之後開始配暫存器以下為程式碼。

|

| 因為超過32位元沒辦法一次寫完,所以我們要自己再寫signal去配置。 |

|

告訴他們key_signal和data_in_signal是相同的只是不同暫存器

|

|

| 將我們自己配置的線路分配到這些暫存器。 |

這樣就寫好囉~那就存檔並且合成吧!

結束之後開始packge ip(記得merge)

過來就一樣開啟舊專案或新專案來放置我們IP,因為只是測試所以我只放新IP要不燃燒錄時間會拖長。(PS:記得在專案內引進自己做得IP哦)

放完就像這樣啦,一樣開始

Generate Output Products->Create HDL warpper

完成後Run Synthesis -> Run Implemented -> Generate Bitstream

跑完就export Hardware-> launch sdk 轉戰SDK囉~

|

| 跟RSA一樣只是drivers變新的IP |

PS:如果是用舊專案可以把原本的底層SDK先刪掉關掉,再去生成比較好友時候生出來還是舊的~3~不知到是不是我的問題。

開一個hello word 專案來測試(記得寫完要燒錄哦!!!!!)

透過程式碼能知道load是告訴程式後面的值還要輸入的開關,mode的開關是加解密開關,start是告訴程式是否已經準備好,done則是做完的時候會立起flag在繼續往下。

一樣連putty測試結果大概是下面降子。

這就是AES 從IP到standalone測試~~有問題歡迎指教。

留言

張貼留言